# **Product Specification Sheet**

## TISG4325S-CD20TB

## **RoHS Compliant GPON SFP OLT B+ Optical Transceiver**

## **PRODUCT FEATURES**

- Single Fiber Transceiver with single mode SC receptacle

- 1490nm continuous-mode transmitter with DFB laser

- 1310nm burst-mode receiver with APD-TIA

- Single 3.3V power supply

- Reset burst-mode receiver design

- Burst mode signal detect output which is LVTTL compatible.

- Burst mode received signal strength indication (RSSI) output

- 20Km Reach 28dB link budget

- Complies with ITU-T G984.2 Class B+

- Digital diagnostic interface compliant with SFF-8472 Rev 9.4 ,

- Complies with RoHS directive (2002/95/EC)

- Operating case temperature: Standard : 0 to +70°C

#### APPLICATIONS

Gigabit Passive Optical Networks (G-PON) - OLT side

#### **PRODUCT DESCRIPTIONS**

The TISG4325S-CD20TB transceiver is the high performance module for single fiber by using 1490nm continuous-mode transmitter and 1310nm burst-mode receiver. It is optical line terminal (OLT) for ITU-T G984.2. The optical transceiver is compliant with the Small Form- Factor Pluggable (SFP) Multi-Source Agreement (MSA).

The transmitter section uses a 1490nm DFB LD with automatic power control (APC) function and temperature compensation circuitry to ensure stable extinction ratio over all operating temperature range. and is Class I laser compliant IEC825 and CDRH standards. The receiver has a hermetically packaged burst-mode APD-TIA (trans-impedance amplifier) pre-amplifier and a burst-mode limiting amplifier with LVPECL compatible differential outputs.

The receiver also includes the function of burst mode signal detect output and fast RSSI output which is enabled by a trigger. When the burst optical power is on, the receiver outputs high level; when the burst optical power is off, the receiver outputs low level. Fast RSSI function can satisfy more severe timing demand to monitor the power from any ONU.

#### ABSOLUTE MAXIMUM RATINGS

| Parameter                  | Symbol  | Min. | Max. | Unit | Note |

|----------------------------|---------|------|------|------|------|

| Storage Temperature        | Tst     | -40  | +85  | °C   |      |

| Operating Case Temperature | Тс      | 0    | 70   | °C   |      |

| Relative Humidity          | RH      | 5    | 90   | %    |      |

| Input Voltage              | -       | GND  | Vcc  | V    |      |

| Power Supply Voltage       | Vcc-Vee | 0    | 3.6  | V    |      |

#### **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol | Min. | Тур | Max. | Unit | Note |

|----------------------|--------|------|-----|------|------|------|

| Supply Voltage       | Vcc    | 3.13 | 3.3 | 3.47 | V    |      |

| Supply Current       | lcc    |      |     | 500  | mA   |      |

| Operating Case Temp. | Тс     | 0    |     | 70   | °C   |      |

## **ELECTRICAL INPUT/OUTPUT CHARACTERISTICS**

#### • Transmitter

| Paramet          | ter          | Symbol          | Min. | Тур | Max. | Unit | Note |

|------------------|--------------|-----------------|------|-----|------|------|------|

| Data input Swing | Differential | V <sub>IN</sub> | 200  |     | 2400 | mV   | 1    |

| Tx Disable       | Disable      |                 | 2.0  |     | Vcc  | V    |      |

| IX DISADLE       | Enable       |                 | 0    |     | 0.8  | V    |      |

| Tx Fault         | Fault        |                 | 2.0  |     | Vcc  | V    |      |

| TX Fault         | Normal       |                 | 0    |     | 0.8  | V    |      |

| Input Diff. Imp  | pedance      | Z <sub>IN</sub> | 90   | 100 | 110  | Ω    |      |

#### • Receiver

| Paramete      | r | Symbol | Min.      | Тур | Max.      | Unit | Note |

|---------------|---|--------|-----------|-----|-----------|------|------|

| Rx LOS Output | Н | VOH    | VccR-1.05 |     | VccR-0.85 | V    | 0    |

|               | L | VOL    | VccR-1.84 |     | VccR-1.60 | v    | 2    |

| PDCT Det      | Н | V_DETH | 2.4       |     | Vcc       |      |      |

| BRST_Det      | L | V_DETL | 0         |     | 0.4       |      |      |

*Note 1)* PECL input, internally AC-coupled and terminated *Note 2)* Internally DC-coupled.

## **OPTICAL CHARACTERISTICS**

#### • Transmitter

| Parameter                               | Symbol | Min.                  | Тур | Max. | Unit | Note |

|-----------------------------------------|--------|-----------------------|-----|------|------|------|

| Operating Wavelength                    |        | 1480                  |     | 1500 | nm   |      |

| Ave. output power (Enabled)             | Po     | 0.5                   |     | 4    | dBm  | 1    |

| Data Rate                               |        |                       | 2.5 |      | Gb/s |      |

| Average Launch Power-OFF<br>Transmitter | Poff   |                       |     | -40  | dBm  |      |

| Rise/Fall time (20%~80%)                | Tr/Tf  |                       |     | 160  | ps   |      |

| Side Mode Suppression Ratio             | SMSR   | 30                    |     |      | dB   |      |

| Extinction Ratio                        | ER     | 10                    |     |      | dB   |      |

| Spectral Width                          | Δλ     |                       | 0.4 | 1    | nm   |      |

| Output Optical Eye                      |        | Compliant with G984.2 |     |      |      |      |

#### Receiver

| Parameter               | Symbol | Min. | Тур  | Max. | Unit | Note |

|-------------------------|--------|------|------|------|------|------|

| Data Rate               |        |      | 1.25 |      | Gb/s |      |

| Operating Wavelength    | λς     | 1260 |      | 1360 | nm   |      |

| Sensitivity             | Psen   |      |      | -29  | dBm  | 2    |

| Receiver Overload       | Sat    | -8   |      |      | dBm  | 2    |

| Receiver CID Tolerance  |        | 72   |      |      | Bit  |      |

| Receiver Reflectance    |        |      |      | -20  | dB   |      |

| Burst Detect De-assert  | BSD_D  | -45  |      |      | dBm  |      |

| Burst Detect Assert     | BSD_A  |      |      | -30  | dBm  |      |

| Burst Detect Hysteresis |        | 1    |      | 6    | dBm  |      |

| Receiver Power DDM (RSSI)<br>Error | RXDDM |  |  | +/-3 | dBm | 3 |  |

|------------------------------------|-------|--|--|------|-----|---|--|

|------------------------------------|-------|--|--|------|-----|---|--|

Note 1) The optical power is launched into SMF.

Note 2) Measured with a PRBS  $2^{23}$ -1 test pattern @1250Mbps, BER  $\leq 1 \times 10^{-10}$ . Note 3) RSSI DDM working range is between -8 to -28 dBm. RSSI DDM accuracy is better than +/- 3dB for input power levels between -12 to -28 dBm, the accuracy reduces to +/- 5 dBm for other input power levels.

#### **DIAGNOSTIC SPECIFICATION**

| Parameter    | Range      | Unit | Accuracy | Calibration         |

|--------------|------------|------|----------|---------------------|

| Temperature  | 0 to +70   | C°   | ±3°C     | Internal / External |

| Voltage      | 3.0 to 3.6 | V    | ±3%      | Internal / External |

| Bias Current | 0 to 100   | mA   | ±10%     | Internal / External |

| Tx Power     | 0 to 5     | dBm  | ±3dB     | Internal / External |

| RX Power     | -30 to -9  | dBm  | ±3dB     | Internal / External |

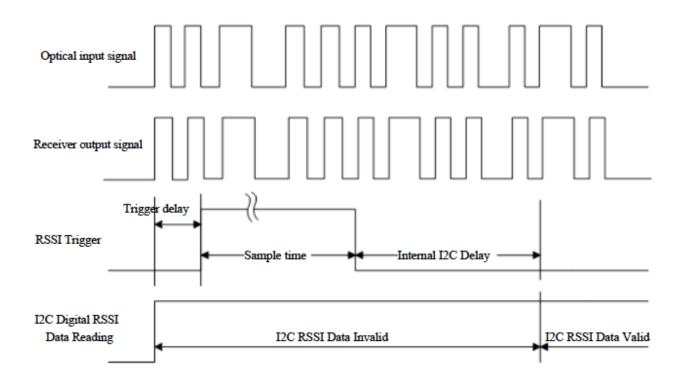

#### TIMING CHARACTERISTICS FOR DIGITAL RSSI

| Parameter          | Symbol | Min. | Тур  | Max.  | Unit |

|--------------------|--------|------|------|-------|------|

| Trigger Delay      | Td     | 30   |      |       | ns   |

| Sample Time        | Ts     | 300  |      |       | ns   |

| Internal I2C Delay | TI2C   |      |      | 500   | ns   |

| Digital RSSI       |        |      | Figu | ire 1 |      |

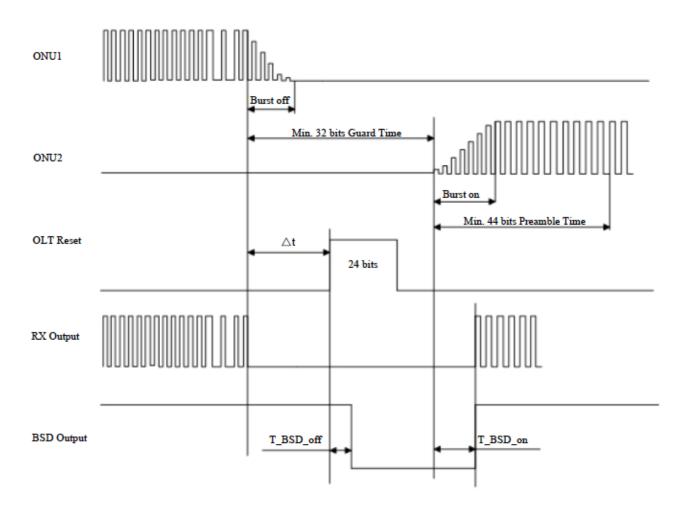

## TIMING CHARACTERISTICS FOR RESET

| Parameter                      | Symbol    | Min.     | Тур   | Max     | Unit |  |

|--------------------------------|-----------|----------|-------|---------|------|--|

| RESET Input Signal<br>(RESET+) | Reset     |          | LVTTL |         |      |  |

| RESET Signal Width             | Tr        |          | 24    |         | Bits |  |

| Guard Timing                   | Tg        | 32       |       |         | Bits |  |

| Preamble Timing                | Тр        | 44       |       |         | Bits |  |

| Reset Delay                    | ∆t        |          |       | Tg - Tr | Bits |  |

| Burst Signal Detect On         | T_BSD_On  |          |       | 20      | ns   |  |

| Burst Signal Detect Off        | T_BSD_Off |          |       | 20      | ns   |  |

| IRESET Timing                  |           | Figure 2 |       |         |      |  |

Figure 2 Reset Timing

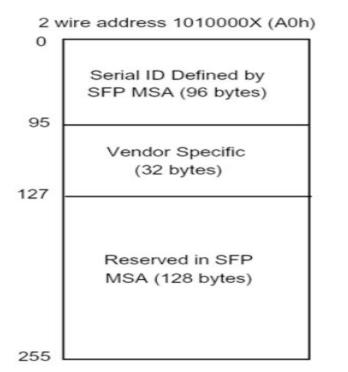

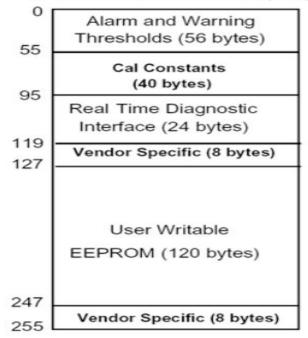

## DIGITAL DIAGNOSTIC MEMORY MAP

The transceivers provide serial ID memory contents and diagnostic information about the present operating conditions by the 2-wire serial interface (SCL, SDA).

The diagnostic information with internal calibration or external calibration all are implemented, including received power monitoring, transmitted power monitoring, bias current monitoring, supply voltage monitoring and temperature monitoring.

The digital diagnostic memory map specific data field defines as following.

2 wire address 1010001X (A2h)

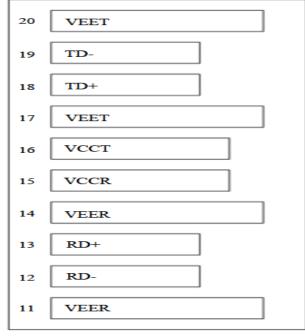

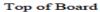

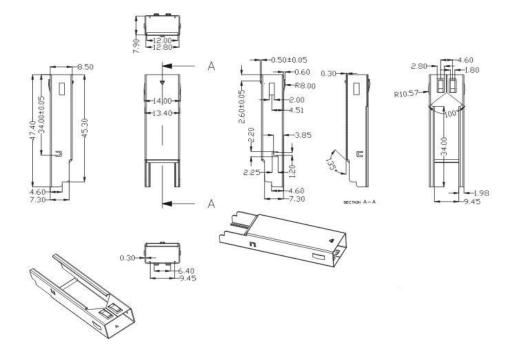

#### **PIN DIAGRAM**

#### **PIN DESCRIPTIONS**

| PIN # | Name             | Function                                                                                           | Plug Seq. | Notes |

|-------|------------------|----------------------------------------------------------------------------------------------------|-----------|-------|

| 1     | V <sub>EET</sub> | Module transmitter ground                                                                          | 1         |       |

| 2     | Tx Fault         | Module Fault Indication                                                                            | 3         | 1     |

| 3     | Tx Disable       | Transmitter Disable;                                                                               | 3         | 2     |

| 4     | MOD_DEF(2)       | SDA Serial Data Signal                                                                             | 3         | 3     |

| 5     | MOD_DEF(1)       | SDA Serial Clock Signal                                                                            | 3         | 3     |

| 6     | MOD_DEF(0)       | TTL Low                                                                                            | 3         | 3     |

| 7     | RESET            | LVTTL input. Assert "Reset" high at the end of<br>previous burst, 16 bits in duration              | 3         | 4     |

| 8     | BSD              | Burst signal detect                                                                                | 3         | 5     |

| 9     | RSSI TRIG        | CMOS input. Assert high at the beginning of the monitored burst package at least 300ns in duration | 3         | 6     |

| 10    | V <sub>EER</sub> | Module receiver ground                                                                             | 1         |       |

| 11    | V <sub>EER</sub> | Module receiver ground                                                                             | 1         |       |

| 12    | RD-              | Receiver inverted data out put                                                                     | 3         | 7     |

| 13    | RD+              | Receiver non-inverted data out put                                                                 | 3         | 7     |

| 14    | V <sub>EER</sub> | Module receiver ground                                                                             | 1         |       |

| 15    | V <sub>CCR</sub> | Module Receiver Power Supply                                                                       | 2         |       |

| 16    | V <sub>CCT</sub> | Module Transmitter Power Supply                                                                    | 2         |       |

| 17    | V <sub>EET</sub> | Module transmitter ground                                                                          | 1         |       |

| 18    | TD+              | Transmitter Data In                                                                                | 3         | 8     |

| 19    | TD-              | Transmitter Inverted Data In                                                                       | 3         | 8     |

| 20    | V <sub>EET</sub> | Module transmitter ground                                                                          | 1         |       |

Plug Seq.: Pin engagement sequence during hot plugging.

1) TX Fault is an open collector output, which should be pulled up with a  $4.7k\sim10k\Omega$  resistor on the host board to a voltage between 2.0V and Vcc+0.3V. Logic 0 indicates normal operation; Logic 1 indicates a laser fault of some kind. In the low state, the output will be pulled to less than 0.8V.

*2)* TX Disable is an input that is used to shut down the transmitter optical output. It is pulled up within the module with a  $4.7k \sim 10k\Omega$  resistor. Its states are:

| Low (0 to 0.8V):      | Transmitter on       |

|-----------------------|----------------------|

| (>0.8V, < 2.0V):      | Undefined            |

| High (2.0 to 3.465V): | Transmitter Disabled |

| Open:                 | Transmitter Disabled |

3) Mod-Def 0,1,2. These are the module definition pins. They should be pulled up with a  $4.7k\sim10k\Omega$  resistor on the host board. The pull-up voltage shall be VccT or VccR.

Mod-Def 0 is grounded by the module to indicate that the module is present Mod-Def 1 is the clock line of two wire serial interface for serial ID

Mod-Def 2 is the data line of two wire serial interface for serial ID

4) RESET is a LVTTL input. When the previous burst signal package is end, the host will give a "high" RESET to restore the state of LA. Internal pull-down 10K resistor to GND.

5) BSD can track the state of receiving burst signal. Logic 0 indicates loss of signal; Logic1 indicates receiving signal packages.

6) RSSI TRIG is a CMOS input. Assert high after 30ns delay time of the beginning of the monitored burst package at least 300ns in duration.

7) RD-/+: These are the differential receiver outputs. They are internally DC-coupled 100 differential lines which should be terminated with  $100\Omega$  (differential) at the user SERDES.

8) TD-/+: These are the differential transmitter inputs. They are internally AC-coupled, differential lines with 100Ω differential termination inside the module.

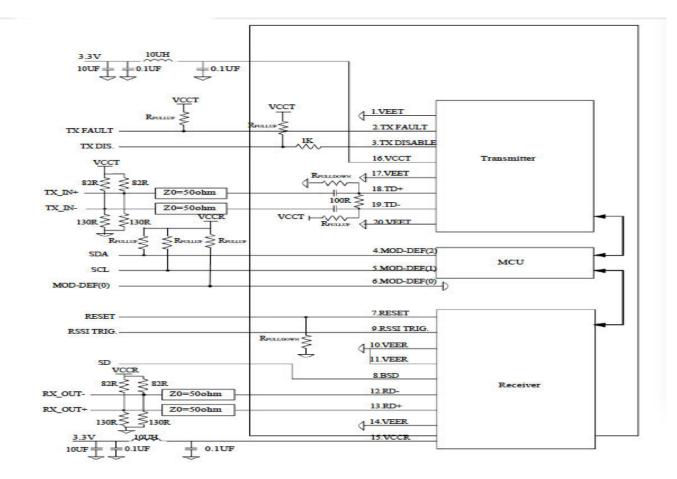

#### **RECOMMENDED INTERFACE CIRCUIT**

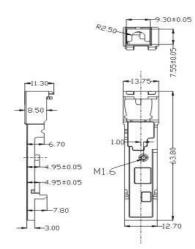

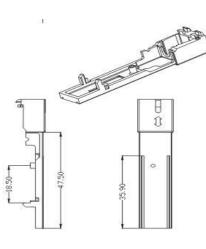

PACKAGE DIMENSIONS

## **ORDERING INFORMATION**

| Part Number      | Description                                                                         |

|------------------|-------------------------------------------------------------------------------------|

| TISG4325S-CD20TC | Tx1490nm/Rx1310nm , 2.5Gbps/1.25Gbps, Class C+, 0°C ~ +70°C With DDM; OLT Type      |

| TISG4325S-CD20TB | Tx1490nm/Rx1310nm , 2.5Gbps/1.25Gbps, Class B+, 0°C $\sim$ +70°C With DDM; OLT Type |

\$